RISC-V Releases Abound Ahead of 2023 RISC-V Summit

At the 2023 North America RISC-V Summit, dozens of presenters will showcase RISC-V innovations in desktop computing and wearable applications.

With industry interest in RISC-V exploding—even forming the core of China’s national plan to cut reliance on Western IP—a full ecosystem has arisen around the open-source ISA. Many of these innovations are slated for presentation at the 2023 RISC-V summit in Santa Clara, California. According to the event's official website, the summit will include keynotes, breakout sessions, and an expo hall supported by key sponsors like Andes Technology, OpenHW Group, and Google.

Andes Technology interview at the RISC-V North America 2022. Screenshot used courtesy of Andes Technology

Ahead of the conference, several big players in RISC-V development have come forward with new releases and collaborations.

Andes Unveils RISC-V Cores for IoT

Andes Technology, a diamond sponsor of the event, is a leading provider of RISC-V IP for SoCs. Recently, the company announced two new RISC-V cores: D23 and N225. Andes says the cores are designed to be as power-efficient yet performant as possible.

Both cores share some critical features but differ in others. For starters, both the D23 and N225 use a 3-stage pipeline, single-issue architecture. Single issue indicates that a single instruction is issued to the pipeline per clock cycle; the Clocks Per Instruction (CPI) is 1. Additionally, both cores are performant, with the D23 featuring 4.55 Coremark/MHz and the N225 achieving 4.4 Coremark/MHz.

Example of a single-issue pipeline architecture. Image used courtesy of IOP Science

A single-issue pipeline architecture includes five pipeline stages: Instruction Fetch (IF), Instruction Decode (ID), Execute (EX), Memory (MEM), and Write Back (WB). For every clock cycle, an instruction in a particular stage of the pipeline advances, and a new instruction is loaded into the pipeline unless it is stalled due to a hazard.

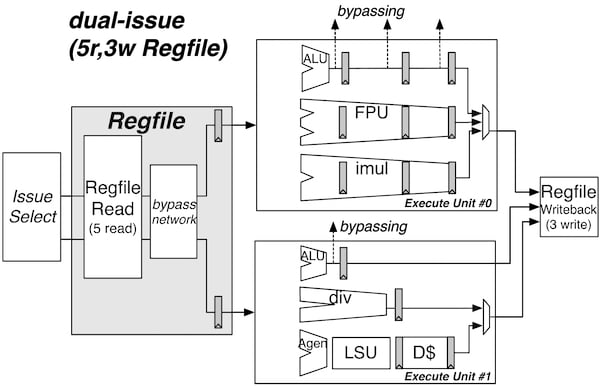

Example of a dual-issue pipeline architecture decode stage. Image used courtesy of RISC-V BOOM

In contrast, a dual-issue architecture includes duplicated logic to execute two instructions at a time. This necessitates additional hardware and, consequently, more power and space requirements on the chip. In its press release, Andes Technology says the two cores are primarily single-issue, with “some dual-issue capability”, but does not elaborate further.

Both cores implement RISC-V extensions—capabilities that can be added to a design to optimize certain characteristics like performance, energy, and area. The D23 core implements certain floating-point extensions that the N225 does not have and includes Supervisor mode for better security. Supervisor mode is a privilege level that allows the execution of higher-privilege code such as kernel code. Such code has access to registers that user-level code does not.

RISC-V privilege levels. Image used courtesy of Stephen Marz

Qualcomm and Google Introduce RISC-V-Based Wearables

In a recent press release, Qualcomm announced that it is partnering with Google to bring RISC-V to the Wear OS platform.

Wear OS powers a variety of Android-based smartwatches. Image used courtesy of Digital Trends

Formerly known as Android Wear, Wear OS is the software behind smartwatches created by various manufacturers, from Samsung to Google itself. Together, Qualcomm and Google aim to create what they call RISC-V Snapdragon Wear, the hardware platform for all future Wear OS wearables. Given the recent announcement, such technology could be showcased at the RISC-V Summit in Santa Clara.

In the past few months, both Google and Qualcomm have been busy in the RISC-V space. In collaboration with other RISC-V leaders (including Andes), Qualcomm and Google recently launched the RISC-V Software Ecosystem (RISE), an effort to develop software for RISC-V cores driving high-level operating systems. Qualcomm has also made strides in RISC-V support by investing in a RISC-V hardware company.

Qualcomm and Google say they will announce the commercial launch of the RISC-V wearable at a later date.

Milk-V Oasis Targets High-Performance AI

Chinese hardware company Milk-V, formally known as Shenzhen MilkV Technology Co., has announced the new Milk-V Oasis, powered by SophGo's SG2380.

Sophgo's SG2380. Image used courtesy of SophGo

The SG2380 is a RISC-V chip with a 16-core CPU, a desktop-level GPU, and a neural processing unit (NPU) in a compact form factor (17 cm x 17 cm). Based on SiFive's P670 and X280 RISC-V processors, the SG2380 offers a reported computational performance of 20 TOPS at INT8, making it a candidate for PCs, tablets, servers, and other computing devices. The SG2380 also features 64 GB of RAM, allowing it to run large-scale LLMs without several AMD or Nvidia accelerator cards.

Since AI applications require a significant amount of computing power, such RISC-V chips are exploding in popularity, signifying a continuing trend of RISC-V adoption in the AI community. Milk-V and SophGo plan to release the SG2380 SoC in nine months and the Milk-V Oasis in 10.

More RISC-V Trends To Be Announced at Summit

The RISC-V Summit North America will take place on November 7–8, 2023, in Santa Clara, California. Industry players, including Andes, Google, Qualcomm, Milk-V, Intel, Microchip, Ventana Micro Systems, Esperanto Technologies, and many more, will share RISC-V breakthroughs, milestones, and case studies to network and build new possibilities for the ISA.